金刚石基GaN器件的技术难点在于金刚石和GaN之间的界面热阻、晶格失配、热应力、CVD生长的纳米晶体金刚石的低导热。CVD生长一般在七八百摄氏度,因为GaN和金刚石的热膨胀系数的差异,当器件冷却到常温时,界面处会有很大的热应力从而使器件破裂。在GaN上面生长金刚石需要一层保护层,这层额外的保护层增加了界面热阻,大大降低了金刚石的散热功效。并且,CVD生长的金刚石在界面附近是纳米晶体,导热系数非常低,只有几十W/m·K。CVD生长几个微米厚之后,多晶体金刚石导热系数才会升高到接近体材料,这一层低质量的金刚石也会阻碍GaN器件散热。

因此,如何将金刚石作为GaN基功率器件的热沉或衬底,成为目前研究热点。目前已经报道了多种技术形式,其中主要有多晶金刚石衬底GaN散热技术、单晶金刚石衬底散热技术、高导热金刚石钝化层散热技术等。

1、多晶金刚石衬底 GaN 散热技术

(1)低温键合技术

键合技术是半导体行业制造过程中重要的技术,绝大部分的电子材料、电子器件结构等连接均会应用到键合技术,可分为高温键合及低温键合两类。

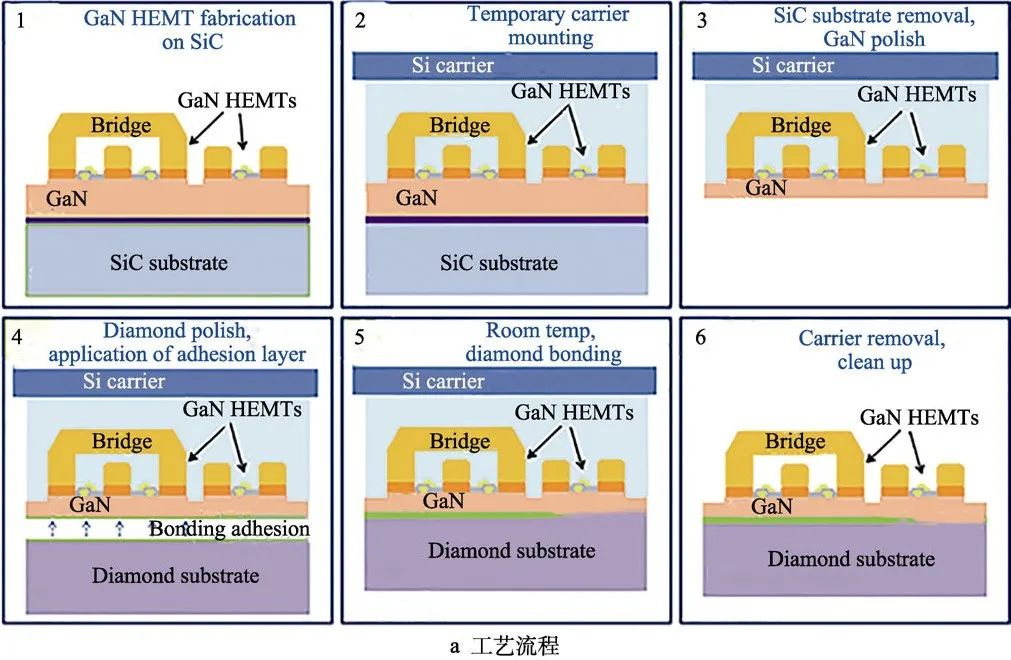

低温键合的基本思路是将GaN外延层从原始的Si衬底上剥离下来,然后在暴露的GaN表面添加中间层,从而与多晶金刚石衬底结合,使GaN基器件的有源区与CVD金刚石衬底接触,降低功率器件结温。

金刚石衬底 GaN 的低温键合技术

(2)基于GaN 外延层背面直接生长金刚石

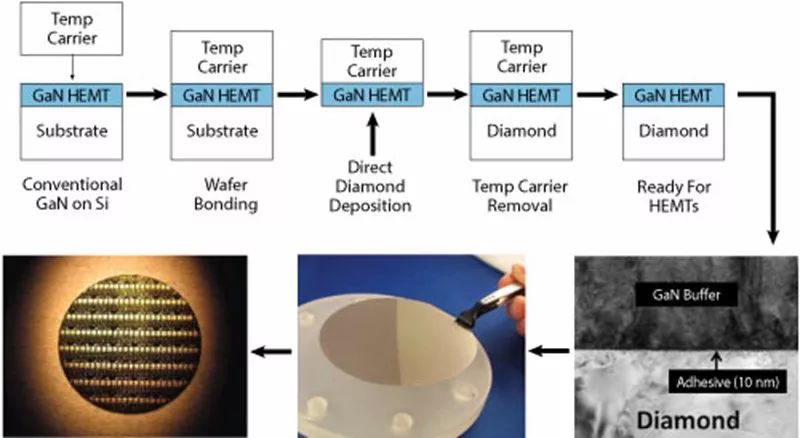

另一种制备金刚石衬底GaN器件的方法,与低温键合技术不同之处是去除衬底及部分GaN缓冲层后在外延层背面首先沉积一层介电层用于保护GaN外延层后再沉积金刚石衬底(厚度~100 μm)。

金刚石晶圆片上GaN的制作过程

2、单晶金刚石衬底外延 GaN

随着单晶金刚石制备技术不断发展和完善,单晶金刚石衬底直接外延 GaN 晶片也被用于改善散热需求。

虽然目前可以实现AINGaN/GaNHEMTs的异质外延。但是难度很大,由于金刚石属于立方结构,GaN属于六方纤锌矿结构,这种晶体结构的差异使单晶金刚石上外延GaN难度极大,另外GaN和金刚石的晶格常数和热膨胀系数差异巨大也对制备带来巨大困难,此外单晶尺寸的限制和成本的限制都进一步影响了其应用。

3、高导热金刚石钝化层散热技术

德国的M.Seelman-Eggebert 从理论和实验两个方面探讨了高热导率金刚石钝化层用于GaN-FETs上热扩散。详细讨论了GaN-FETs工艺条件与低温沉积金刚石的工艺兼容性,并采用选择性低温(沉积温度400℃)生长金刚石膜的方法在GaN-FETs的栅极上沉积0.7 μm厚的金刚石膜,对比沉积金刚石膜前后晶体管的输出特性和传输特性变化不明显,认为这是第一次可以在Ⅲ-Ⅴ族半导体晶体管器件上直接沉积金刚石用于热扩散,但具体的金刚石冷却效果并未进行验证。

尽管高导热金刚石钝化层散热技术具有巨大潜力,但是在制作HEMTs过程中,沉积纳米金刚石薄膜往往受到器件工艺条件的限制,沉积温度一般较低,纳米金刚石膜的热导率并不高,这些都限制了该技术的应用和推广。

化合积电致力于金刚石半导体材料生产研究,采用MPCVD法制备出 1-4英寸金刚石晶圆,生长表面粗糙度Ra<1nm,热导率1000- 2000W/(m·K),基本满足金刚石与硅、氮化镓、磷化铟、氧化镓等半导体材料键合,对尺寸、热导率及表面光洁度及面形度等方面的基本要求。