在半导体器件尺寸持续缩小至10纳米以下的时代,电学表征技术面临严峻挑战:传统扫描探针显微镜(SPM)虽能实现纳米级分辨率,但其依赖手动更换探针的操作严重制约了测量效率。尤其对于扫描扩展电阻显微镜(SSRM)这类技术,探针需同时满足超高机械强度(承受10 GPa接触压力)、纳米级锐度(尖端半径<5 nm)和高导电性,而现有涂层金刚石探针(CDT)和全金刚石探针(FDT)均存在性能短板。更棘手的是,探针锐度提升往往伴随磨损加剧,进一步加剧了频繁更换的需求。

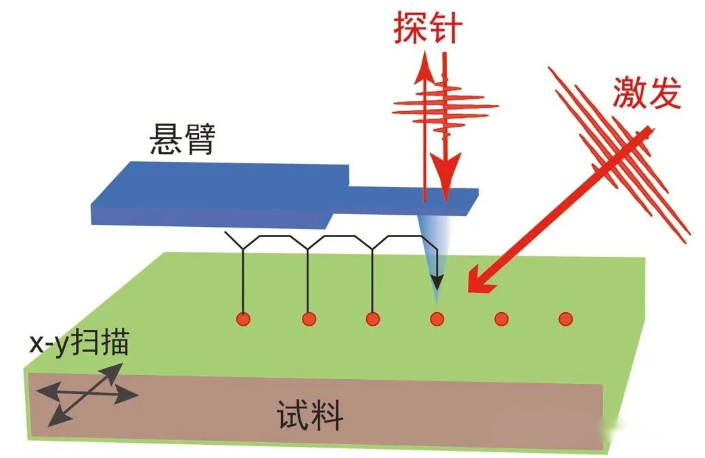

针对这一瓶颈,研究人员创新性地提出反向探针样品扫描探针显微镜(RTS SPM)架构——将样品固定在无探针悬臂上扫描固定探针阵列,从而通过快速切换探针实现高通量测量。然而,该技术的核心瓶颈在于缺乏适配的探针芯片:现有硅基阵列探针锐度不足,而传统单尖金刚石探针制备工艺无法直接用于高密度阵列集成。

通过KOH各向异性刻蚀制备倒金字塔硅模具;生长硼掺杂金刚石薄膜;结合金属电镀支撑膜与选择性硅衬底腐蚀实现阵列释放;最终通过自图案化干法刻蚀在金字塔基底上生成纳米级锐化多尖结构。工艺优化后,探针阵列密度达792尖/芯片,尖端半径最小2.7 nm,间距25-30 μm满足RTS悬臂安全扫描需求。

研究结果显示,HFDT芯片在p型硅阶梯校准样品测量中展现出优异动态范围(1016-1019 carriers/cm3),证实其导电性与机械稳定性。在GaAs纳米脊波导结构中,HFDT探针成功解析了纳米级异质界面。与CDT芯片的对比实验更具说服力:测量28 nm栅长FinFET时,HFDT将栅极宽度测量误差从CDT的模糊成像精确至27 nm,并清晰呈现源漏外延(S/D epi)掺杂扩散轮廓,这对器件建模至关重要。

该研究的突破性在于首次将HFDT技术成功移植到RTS探针芯片架构,通过四锚点设计解决膜应力变形,利用自图案化刻蚀实现规模化纳米尖制备。相比传统CDT芯片,HFDT芯片将SSRM空间分辨率提升至与常规SSRM相当水平,同时保留RTS技术5倍通量优势。

化合积电是一家专注于宽禁带半导体材料研发、生产和销售的国家高新技术企业,核心产品有多晶金刚石(晶圆级金刚石、金刚石热沉片、金刚石窗口片、金刚石基复合衬底)、单晶金刚石(热学级、光学级、电子级、硼掺杂、氮掺杂)和金刚石复合材料等,引领金刚石及新一代材料革新,赋能高端工业化应用,公司产品广泛应用于激光器、GPU/CPU、医疗器械、5G基站、大功率LED、新能源汽车、新能源光伏、航空航天和国防军工等领域。