随着传统平面晶体管缩放技术达到极限,3D集成封装技术已成为“延长”或“推进”摩尔定律的有力解决方案。通过垂直堆叠芯片,该技术可在更小的占用面积内实现更高的晶体管密度,实质上为芯片设计引入了第三维度。过去十年间,3D异构集成与先进封装技术取得了显著进展。这些创新通过堆叠并互联不同功能模块,有效缩短了电气互联长度,从而提升了片上带宽、加快了互联通信速度并降低了整体功耗。

热管理挑战源于3D堆叠,因为每增加一层,热阻就会累积,而距离散热结构最远的组件通常具有最长的热传导路径。在芯片间界面存在显著的热瓶颈,其中两层堆叠芯片之间的热阻(包括微凸点和传统填充材料)仍相对较高(4W/mK至15W/mK)。这些热限制会影响系统性能,包括工作频率和热设计功耗(TDP),尤其在多层堆叠配置中。

为解决3D封装中的热瓶颈问题,行业长期以来一直在寻找兼容CMOS和封装技术的材料,这些材料需同时具备优异的电气绝缘性能和高热导率。金刚石具有极端物理特性,近期被视为3D异构集成系统封装应用中下一代跨芯片材料的候选者。单晶金刚石(SCD)具有良好的电气绝缘性(3.47 eV 带隙),高击穿场强(2×10⁷ V/cm)和热导率(2200 W/m·K),以及较低的介电常数(5.5)。然而,目前SCD的制备面积小,且成本极高。另一方面,近期研究表明,多晶金刚石薄膜(PCD)可实现高达1800W/mK的热导率,且制备成本低廉,可在低温(300−400∘C)下制备。

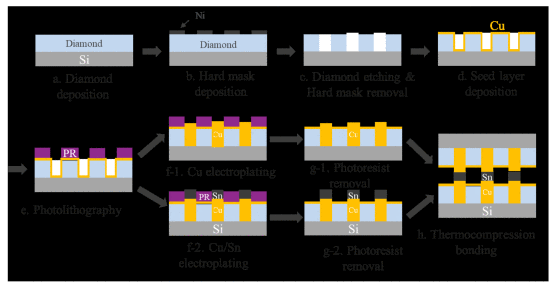

近期,由美国普渡大学发表了“Inter-Die Hybrid Cu/Diamond Microbump Bonding for 3D Heterogenous Integration”论文,研究提出了一种新型铜/金刚石微凸点键合技术,旨在降低3D异构系统中的芯片间热阻。该工艺首先沉积8μm厚的聚晶金刚石(PCD)薄膜,随后通过氧等离子体刻蚀形成圆柱形孔洞。Cu/Sn微凸点通过电镀工艺填充刻蚀区域,最后通过倒装芯片热压 bonding 完成 bonding 过程。该 bonding 架构在界面层中集成了金刚石热扩散层,显著提升了堆叠芯片间的高通孔和面内热导率。尽管当前结果证明了该方法的可行性,但在制造过程中仍发现若干挑战,特别是光刻胶涂覆均匀性及其对微凸点键合质量和机械性能的影响。

这种新型铜/钻石混合键合技术在解决3D异构集成中的热管理挑战方面代表了重大进展,有望在下一代电子系统中实现更高的功率密度和改进的热性能。所开发的工艺流程为未来在先进封装应用中研究钻石集成热管理解决方案奠定了基础。

化合积电专注于金刚石热管理材料解决方案,为广大客户提供全面的金刚石热管理材料,包括金刚石热沉片、金刚石晶圆衬底、金刚石光学窗口、金刚石复合材料等,欢迎进行详洽。