金刚石凭借其极高的各向同性热导率(λ),作为有效芯片冷却的散热片极具前景。过去几十年里,为促进金刚石散热片的应用,人们开展了多种尝试,包括:在金刚石上外延生长半导体,或通过化学气相沉积(CVD)直接在半导体上生长多晶金刚石,以及将金刚石键合到半导体。然而,现有方法存在诸如高工艺温度/压力和大热阻等挑战。金刚石的直接生长通常需要超过400℃的高温,这对与现代芯片封装工艺的兼容性构成挑战。而传统芯片贴装技术(如焊接和银烧结)往往会引入显著的热阻。

通过纳米层金属再结晶成功实现金刚石与硅的低温键合,并将其集成到最先进的玻璃中介层封装中,玻璃中介层上的芯片-金刚石(DoCoG)封装实现了显著改善的冷却性能。

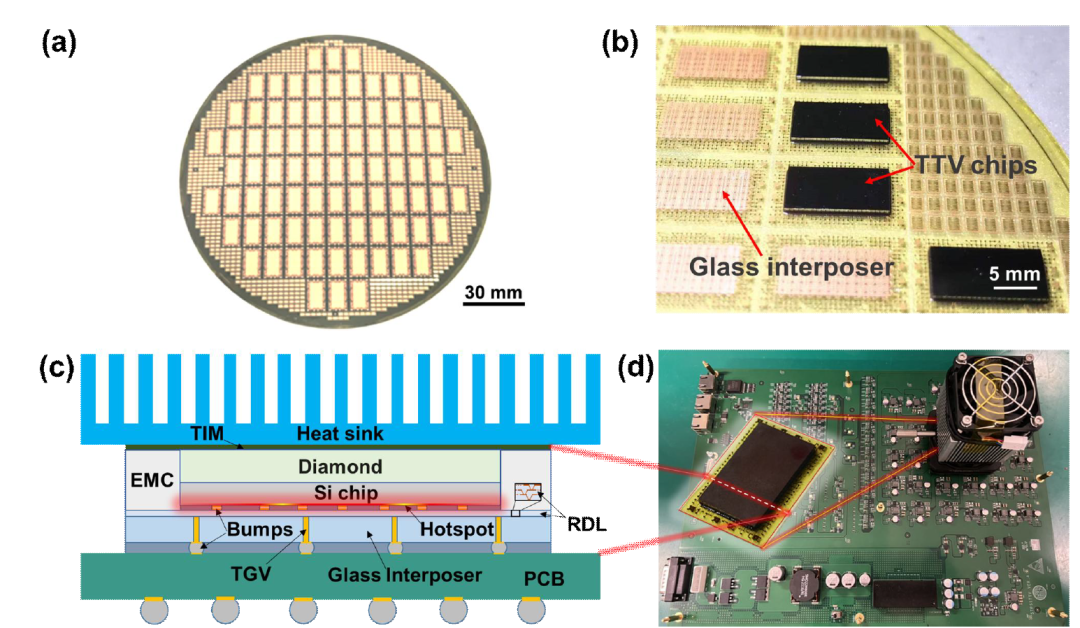

玻璃中介层采用6英寸晶圆制造,如图1所示。在200微米厚的AF32玻璃晶圆上,通过激光诱导湿法蚀刻制作玻璃通孔(TGV)。沉积0.5微米钛/2微米铜种子层用于双面铜电镀;此后,通过化学机械抛光(CMP)去除多余铜。光刻及电镀在两侧进行,以制造再分布层(RDL)。涂覆了介质层,并通过光刻技术暴露出铜垫。

图1. (a)用于金刚石/芯片封装的带有穿玻璃通孔(TGV)和再分布层(RDL)的6英寸玻璃中介层。(b)玻璃中介层晶圆上的芯片到晶圆键合。(c) 芯片上金刚石玻璃中介层(DoCoG)集成示意图。(d) DoCoG封装热测试配置的照片。

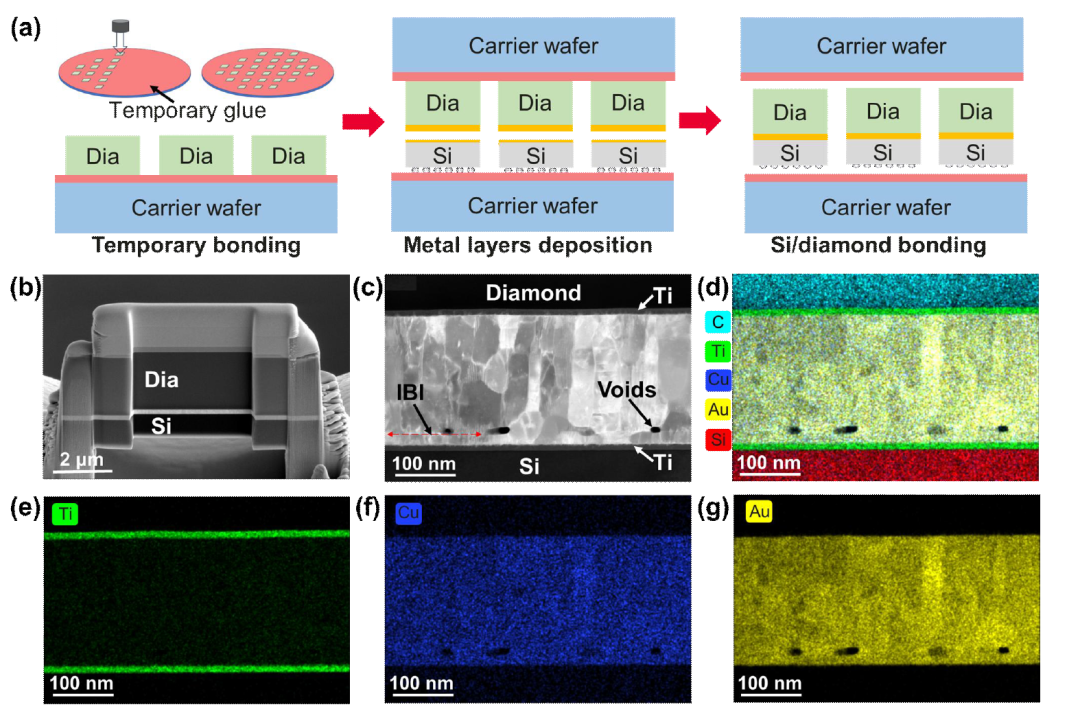

低温硅/金刚石键合涉及将硅芯片(带有Sn3.5Ag焊料凸点)和多晶金刚石基板(尺寸为12毫米 x 6毫米 x 400微米)组装到载片上,使用临时粘合剂在室温下施加约0.5兆帕的压力(图2(a)),如参考文献[25]中先前描述的那样。金刚石和芯片都以相同的对齐模式组装成集体晶圆。硅和金刚石的表面经过仔细清洁。随后,设计了金属层,包括在金刚石上的8纳米Ti/200纳米Cu/5纳米Ti/20纳米Au层以及在硅上的8纳米Ti/20纳米Au层。最外层由纳米层金涂层组成,能够在室温下实现预键合。加入了铜中间层以促进Cu-Au冶金反应并增强键合可靠性。热边界电阻(TBR)的主要贡献来自于金属/金刚石界面,而Cu/金刚石界面的TBR据报道是Ti/金刚石界面的三倍。在此,使用了钛粘附层来最小化金刚石/金属界面的TBR并增强粘附强度。此外,我们引入了具有高λ和纳米级厚度的反应性Cu/Au层以降低热阻。这些技术共同旨在降低金刚石和硅之间的TBR。金刚石基板通过对准晶圆对准在相应的芯片顶部对准,然后通过Au-Au冷焊在室温下预键合,接着在200摄氏度下施加3兆帕的压力进行30分钟的键合。随后剥离载片,形成用于后续芯片到晶圆玻璃中介层封装的金刚石/芯片键合对。低温和低压键合条件防止了对焊料凸点的不可修复损坏,这些焊料凸点在回流后恢复到原来的外观。

硅与金刚石材料之间形成了均匀的金属键合层,如图2(b)所示。初始键合界面(IBI)存在一些残余空洞,在铜-金-钛互扩散和冶金反应的促进下经历了固结与再结晶过程。这一点通过图2(c)的透射电子显微镜(TEM)分析以及图2(d)~(g)的能量色散谱(EDS)得到证实。

这种芯片贴装技术具有低键合温度同时维持高重熔温度的优势(根据相图,CuAu中间层金属的重熔温度理论上超过900 ℃)。因此,它能够承受后续约260 ℃的多次焊料回流。

图2(a)金刚石与硅芯片通过焊料凸点键合过程的示意图。(b)金刚石/硅键合线的扫描电子显微镜(SEM)分析和(c)透射电子显微镜(TEM)分析。(d)~(g)碳(C)、硅(Si)、钛(Ti)、铜(Cu)和金(Au)元素的能量色散X射线光谱(EDS)映射。

采用基于文献特别设计的硅基热测试载具(TTV)来表征金刚石集成芯片的热性能。TTV芯片尺寸为12 mm×6 mm×200 μm,利用我们优化的键合技术与400 μm厚的金刚石(热导率λ约1500 W/m·K)键合。如图1(a)和(b)所示,TTV/金刚石样品通过带底部填充料的倒装焊键合到玻璃中介层上;随后,中介层晶圆用环氧模塑料(EMC)进行压缩成型。研磨去除金刚石背面的多余EMC材料以利于散热。封装晶圆经过凸点制作、切割等后续工艺。图1(c)展示了测试封装的结构:利用热界面材料(TIM)在金刚石散热器上安装风冷散热器,最终将热量散发至周围环境(图1(d))。此外,还测试了未集成金刚石的600 μm厚TTV芯片作为基线对照。

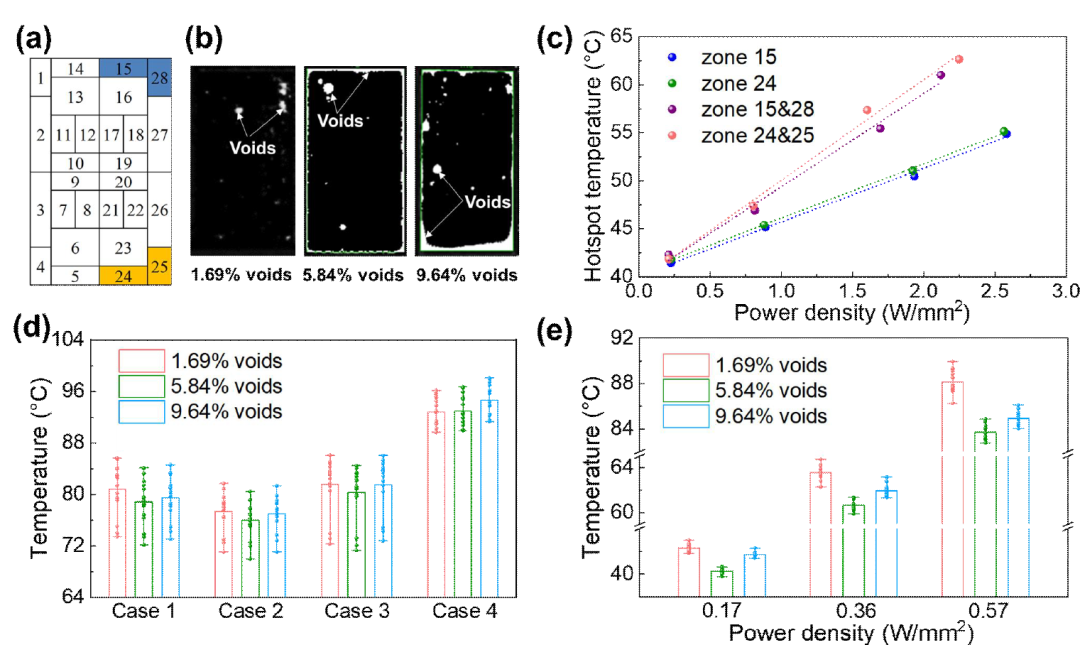

对于编号21至28的区域,两个基本单元的加热电阻器被串联合并,但其热传感器未合并。因此,28个区域可独立控制加热,36个热传感器可用于温度检测。

图3(a)TTV晶圆具有一个含28个可独立控温的结区加热层。(b)金刚石/TTV晶圆的键合界面存在空洞缺陷。(c)不同功率密度下的最高热点温度分布。(d)和(e)分别为不同键合孔隙率下,采用局部高热流密度加热与全局均匀热流密度加热时的实测温度分布。

对金刚石/总厚度变化(TTV)芯片键合界面的扫描声学显微镜检查显示,界面存在随机气泡形成的空洞。这些空洞预计会充当热绝缘体,导致传热受阻。因此,研究了键合空洞对整体冷却性能的影响。测试并分析了不同孔隙率(1.7%、5.8%和9.6%)的样品,如图3(b)所示。图3(c)展示了当孔隙率为9.6%的金刚石/TTV在不同区域选择性加热时的热点温度——其中3号区及3&4号区空洞较少,13号区及13&14号区空洞更明显。测量结果表明,这些不同孔隙率的区域对温度分布的影响极小。

进一步在局部高热流(热点热流条件见表I)和不同功率密度的全局均匀加热条件下开展测试,结果分别如图3(d)和图3(e)所示。温度分布相对一致,观测到的变化很小。这些发现表明,孔隙率小于10%的空洞对冷却能力影响极小。这可归因于键合金属层的热导率(λ)比空洞高出几个数量级,热量主要通过金属层旁路传递。

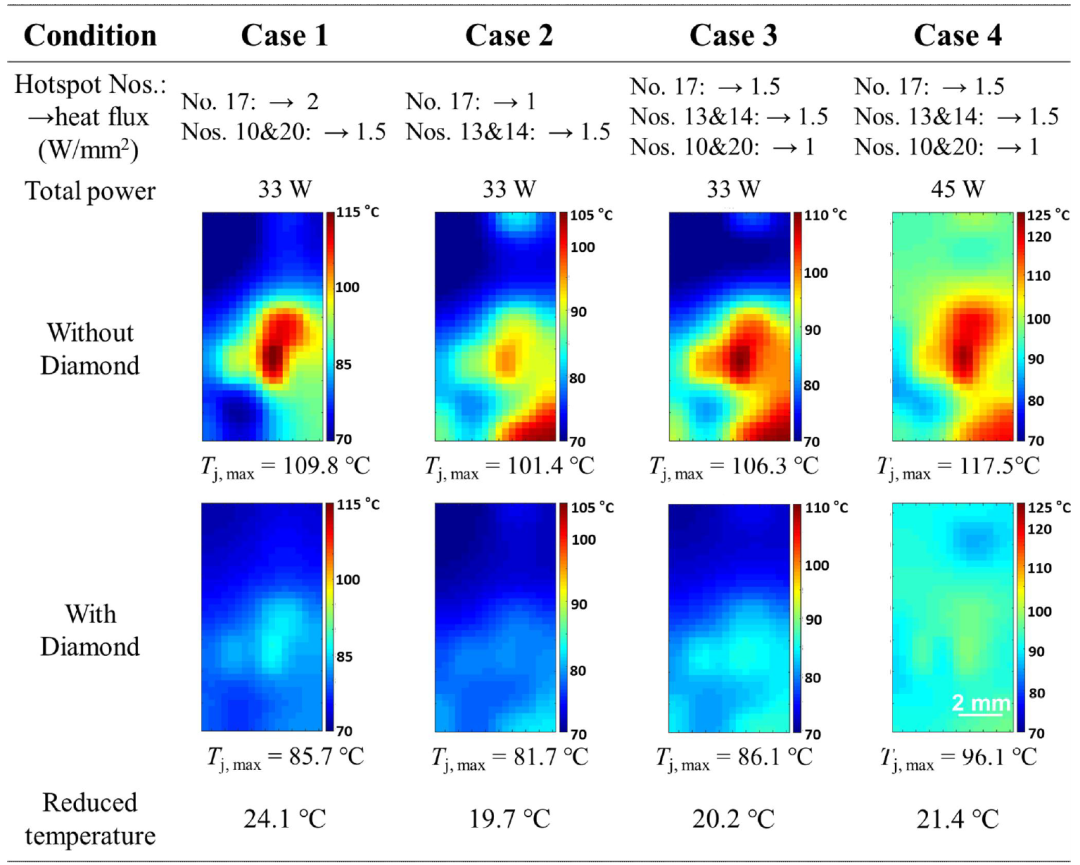

将DoCoG封装的热性能与无金刚石集成的封装进行对比。在局部高热流加热条件下开展了4组测试案例,以模拟真实微处理器[8,29],如表I所示。这些图像基于离散传感器的实测温度生成2D等高线图。案例1中,TTV芯片近中心核心区域的局部热点最大功率密度约为2 W/mm²时,最大结温降低了24.1 ℃;背景功率密度约为0.2 W/mm²,对应总功耗约33 W。由于集成了金刚石,结到环境的热阻从2.6 ℃/W降至1.8 ℃/W,降幅达28.5%。在案例2和案例3中,热点最大热流相似(均为1.5 W/mm²)但位置不同,最大温度降幅均约为20 ℃。案例4中,热流密度较案例3增加,对应总功耗约45 W,温度降幅略增至21.4 ℃。

表格I 不同热通量条件下的测量温度

将降低的热点温度与芯片的先进冷却技术进行对比。具体而言,对于200 μm厚的硅芯片搭配400 μm厚的金刚石,纳米银烧结技术在尺寸为3×0.5 mm²、热流密度高达15 W/mm²的热点处实现的最大温度降幅为14.1 ℃;相比之下,金锡焊接技术在尺寸为0.45×0.3 mm²、热流密度为9.3 W/mm²的热点处仅实现5.2 ℃的最大温度降幅。近期开发的高性能跳跃液滴蒸汽室在热流密度为2 W/mm²的热点处实现的温度降幅<12.3 ℃;主动热电冷却器在尺寸为0.4×0.4 mm²、热流密度高达13 W/mm²的热点处报告的最高温度降幅为15.8 ℃。这些结果表明,金刚石集成封装实现了更优的冷却性能。